The number is calculated as a ratio of the total cell area for hard macros and standard cells or soft macro cells to the core area. A core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left free for routing.

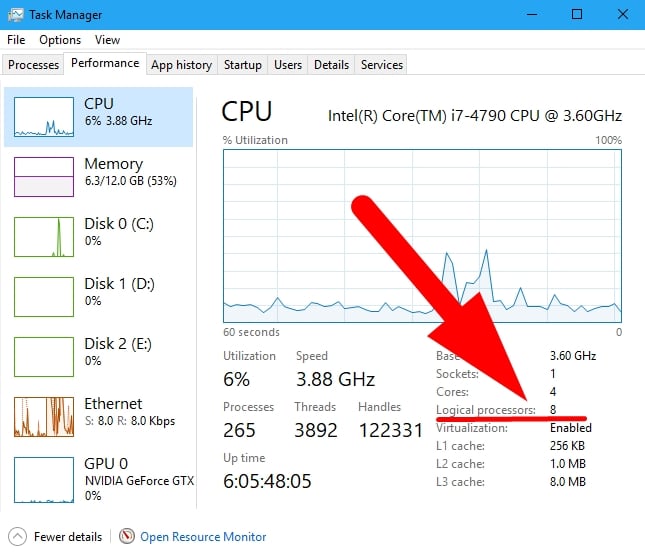

Cpu Cores Vs Logical Processors Threads

Left bottom right top.

. Then partitioning was done to divide the chip into small blocks after that. Physical Design Flow Mohammad reza Kakoee micrellab mkakoeeuniboit Physical Design Flow Mohammad reza Kakoee micrellab mkakoeeuniboit. Posted by Akshay at 2116.

Quality of your Chip Design implementation depends on how good is the Floorplan. To further change the shape of the floorplan you must set the. 50 The Cell Utilization ie Standard Cell Utilization A.

IO pins vs Pads 1. The tool determines the location of each of the components in digital design. Generally pad placement and pin placement is.

Adjust the length of the sides if needed by changing the arguments to the-side_ratio or-side_length options and reissue the initialize_floorplan command. Given the design at right with a single buffer that is relatively tiny and a large macro that occupies half of the design and what is. Core utilization standard cell area macro cells area total core area.

Physical Design Implementation of Single Core 32 Bit RISC Processor on 28nm Technology. Cell Utilization Q. Create physical shape of power domains which is defined in the UPF we have committed.

As a result physical design plays a critical part in the VLSI design flow. Icc2_shell initialize_floorplan -core_utilization 07 -shape L -orientation N -side_ratio 1 1 1 1 -core_offset 1000 -flip_first_row true -coincident_boundary true 2. A good floorplan can be make implementation process place cts route timing closure cake walk.

Online Process Safety Course in Noida. On similar lines a bad floorplan can create all kind issues in the design. Core Utilization defines the area occupied by standard cell macros and blockages.

Core utilization macros area std cell area pads area total core area Pad placement. Core size Standard cell area Utilization Assuming there are no hard macros. Define D fi core area.

If core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left for routing. In ASIC design three types of IO Pads. You can specify a boundary and ask the tool to honour it.

Core-to-IO spacing Can also specify core andor die IO pad dimensions Defaults. On Physical Design Flow IIPlacement. Rcr Row area Core area H x V.

2 every other row. It indicates the amount of channel space to provide for routing between the cell rows. Ll utilization f cells ili i factor IO Analog macro g core core IO Shape can be implied by a macro Place IO fixed equidistant Take macros and power.

Core utilization allowed eg07 ie70 Calculations. We consider both the hard macros and standard cells. Thank you for sharing this.

Total standard cell area no. Physical Design Implementation of Single Core 32 Bit RISC Processor on 28nm Technology Feroz Ahmed Choudhary1 Amay Shiva Naik2 Dr. After you have done floorplanning ie.

Core UtilizationCu Standard Cell areaRow area Channel area Row to Core Ratio Rcr. The Core Utilization. ASIC Physical Design Standard-Cell Design Flow Using the Cadence Innovus Digital Implementation System.

Physical design electronics In integrated circuit design physical design is a step in the standard design cycle which follows after the circuit design. 70 of the core. A core utilization of 08 for example means that 80 of the core area is used for cell placement and 20 percent is available for routing.

If the name of a cell is not present in the current design it will consider as physical only cells. Created the core area placed the macros and decided the power network structure of your design it is time to let the tool to do standard cell placement. Floorplan is one the critical important step in Physical design.

We define core margin by Core to IO boundary or Core to Die boundary. The smaller the number the more space is left for routing. Morikus Tech January 21 2022 at 350 PM.

Core utilization physical design Should you be a enthusiast of nail artwork but will not be utilized to the various coats of acrylic then this sort of design could just do the job properly for yourself. A value of 10 leaves no routing channel space. Core utilization standard cell area macro cells area total core area A core utilization of 08 means that 80 of the area is available for placement of cells whereas 20 is left free for routing.

The objective of this PG Diploma course is to provide the candidates with the best Detail knowledge and skills in the Process Safety Engineering discipline to facilitate faster learning curves while on the job. If there are then add this also X um Y um. Cell row flip from bottom up Initiate floorplanning and generate tracks.

We consider only the standard cells the hard macros will be neglected. Community Guidelines The Cadence Design Communities support Cadence users and technologists interacting to exchange ideas news technical information and best practices to solve. Core Utilization standard cell area macro cells areapad area total core area.

IOPin placement IO Pins are placed at the boundary of the chipPin Placement is an important step in floorplanning. Creating and developing a physical model of the design in the form of an initial optimized layout Because floorplanning significantly affects circuit timing and performance especially for complex hierarchical designs the quality of your floorplan directly affects the quality of your final design Calculation of Core Die size and Aspect Ratio. When the number of routing tracks available for routing in a given location is less than the number necessary the area is considered congested and hence is termed as congestion in VLSI Physical Design Flow.

At this step circuit representations of the components devices and interconnects of the design are converted into geometric representations of shapes which when manufactured in the. Ratio and utilization factor and then based on the macros present we placed the macros in smart way so that in further stages there are no congestions. We define Core Size By or Die Size By where core size by is defined by aspect ratio HeightWidth and core utilization or dimension where we define height and width of core.

Of standard cells one standard cell area Alternatively this can be directly obtained from the DC area report. The number of nets that may be routed through a given region. Core utilization percentage indicates the amount of core area used for cell placement.

Buffer Utilization An Overview Sciencedirect Topics

Fpga Vs Asic Differences Between Them And Which One To Use Numato Lab Help Center

Design Is Intelligence Made Visible In 2021 Design Glass Allusion

Multi Core Architectures An Overview Sciencedirect Topics

Stages Of Automation Maturity Cyber Physical System Advanced Robotics Digital Transformation

0 comments

Post a Comment